Correo:info@anke-pcb.com

WhatApp/WeChat: 008618589033832

Skype: Sannyduanbsp

Tres aspectos para asegurar a integridade da potencia enDeseño de PCB

No deseño electrónico moderno, a integridade de enerxía é unha parte indispensable do deseño de PCB. Para garantir o funcionamento estable e o rendemento dos dispositivos electrónicos, debemos considerar e deseñar de xeito comprensivo desde a fonte de enerxía ata o receptor.

A través do deseño e optimización de módulos de potencia, planos de capas interiores e chips de alimentación podemos conseguir realmente a integridade do poder. Este artigo afondará nestes tres aspectos clave para proporcionar orientación e estratexias prácticas para os deseñadores de PCB.

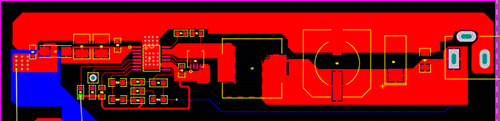

I. Cableado de disposición do módulo de potencia

O módulo de potencia é a fonte de enerxía de todos os dispositivos electrónicos, o seu rendemento e a súa disposición afectan directamente á estabilidade e á eficiencia de todo o sistema. O esquema e o enrutamento correctos non só poden reducir as interferencias de ruído, senón tamén asegurar un fluxo de corrente suave, mellorando así o rendemento global.

2. Disposición do módulo de potencia

1. Procesamento de seguimento:

O módulo de enerxía debe prestarlle especial atención xa que serve como punto de partida do poder. Para reducir a introdución de ruído, o ambiente arredor do módulo de potencia debe manterse o máis limpo posible para evitar a adjacencia a outrosAlta frecuenciaou compoñentes sensibles ao ruído.

2.Close ao chip de fonte de alimentación:

O módulo de potencia debe situarse o máis preto posible do chip subministrado de enerxía. Isto pode reducir as perdas no proceso de transmisión actual e reducir os requirimentos da área do plano da capa interna.

3. Consideracións de disipación de calefacción:

O módulo de potencia pode xerar calor durante o funcionamento, polo que debería asegurarse de que non haxa obstrucións por encima da disipación de calor. Se é necesario, pódense engadir disipadores de calor ou ventiladores para o arrefriamento.

4.Voiding Loops:

Ao enrutar, evite a formación de bucles actuais para reducir a posibilidade de interferencias electromagnéticas.

II. Planificación do deseño do plano de capa interior

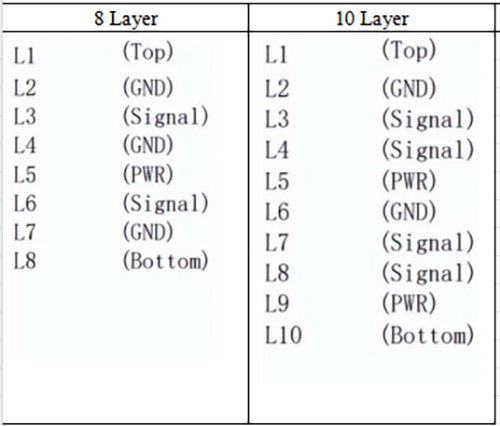

A. Deseño de pila de capas

In PCB EMC Design, o deseño de pila de capas é un elemento clave que debe considerar o enrutamento e a distribución de enerxía.

A. Para garantir as características de baixa impedancia do plano eléctrico e absorber o acoplamiento de ruído do chan, a distancia entre os planos de potencia e terra non debe exceder os 10 quilómetros, normalmente recomendada para ser inferior a 5 millóns.

b. Se non se pode implementar un único plano de enerxía, pódese usar unha capa de superficie para establecer o plano de alimentación. Os planos de potencia e terra moi adxacentes forman un condensador de plano con mínima impedancia de CA e excelentes características de alta frecuencia.

c. Evite dúas capas de alimentación adxacentes, especialmente con grandes diferenzas de tensión, para evitar o acoplamiento de ruído. Se é inevitable, aumenta o espazo entre as dúas capas de alimentación o máximo posible.

d. Os planos de referencia, especialmente os planos de referencia de potencia, deberían manter características de baixa impedancia e pódense optimizar mediante condensadores de desvío e axustes da capa.

B. Segmentación de potencia Multiple

A. Para fontes de enerxía específicas de pequeno rango, como a tensión de traballo núcleo dun certo chip IC, o cobre debe colocarse na capa de sinal para garantir a integridade do plano de enerxía, pero evite colocar o cobre de potencia na capa superficial para reducir a radiación de ruído.

b. A selección do ancho de segmentación debería ser adecuada. Cando a tensión é superior a 12V, o ancho pode ser de 20-30 quilómetros; Se non, elixe 12-20 millóns. Hai que aumentar o ancho de segmentación entre fontes de enerxía analóxica e dixital para evitar que a potencia dixital interfire coa potencia analóxica.

c. As redes de enerxía sinxelas deben completarse na capa de enrutamento e as redes de potencia máis longas deberían ter engadidos os condensadores de filtro.

d. O plano de enerxía segmentado debe manterse regularmente para evitar formas irregulares provocando resonancia e aumento da impedancia de potencia. Non se permiten tiras longas e estreitas e divisións en forma de pesas.

C. Filtrado de planos

A. O plano eléctrico debe estar estreitamente unido ao plano terrestre.

b. Para chips con frecuencias de funcionamento superiores a 500MHz, dependen principalmente do filtrado de condensadores de plano e usa unha combinación de filtrado de condensadores. O efecto de filtrado debe ser confirmado mediante simulación de integridade de enerxía.

c. Instale os indutores para condensadores de desacoplamiento no plano de control, como ampliar o condensador e aumentar as vías do condensador, para asegurarse de que a impedancia do chan de potencia sexa inferior á impedancia obxectivo.

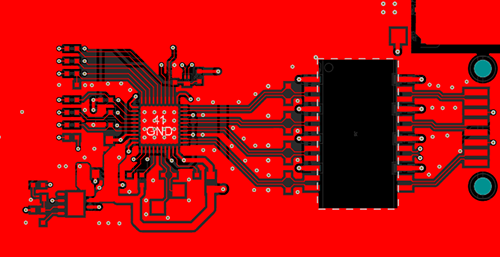

Iii. Cableado de disposición de chip de enerxía

O chip de enerxía é o núcleo dos dispositivos electrónicos e asegurar que a súa integridade de enerxía sexa crucial para mellorar o rendemento e a estabilidade do dispositivo. O control de integridade de enerxía para os chips de enerxía implica principalmente enrutamento de manexo de pasadores de alimentación e disposición correcta e cableado de condensadores de desacoplamiento. O seguinte detallará consideracións e consellos prácticos sobre estes aspectos.

A. CHIP POWER PIN enrutando

O enrutamento de pinos de alimentación de chip é unha parte crucial do control de integridade de enerxía. Para proporcionar unha subministración de corrente estable, recoméndase engrosar o enrutamento de pasadores de enerxía, xeralmente ao mesmo ancho que os pasadores de chip. Normalmente, oAncho mínimoNon debería ser inferior a 8 millóns, pero para obter mellores resultados, intente conseguir un ancho de 10 millóns. Ao aumentar o ancho do enrutamento, pódese reducir a impedancia, reducindo así o ruído de potencia e garantindo o subministro de corrente suficiente ao chip.

B.Layout e enrutamento de condensadores de desacoplamiento

Os condensadores de desacoplamiento xogan un papel significativo no control de integridade do poder para os chips de enerxía. Dependendo das características do condensador e dos requisitos de aplicación, os condensadores de desacoplamiento xeralmente divídense en condensadores grandes e pequenos.

A. Grandes condensadores: os condensadores grandes normalmente distribúense uniformemente arredor do chip. Debido á súa menor frecuencia resonante e ao radio de filtrado maior, poden filtrar eficazmente o ruído de baixa frecuencia e proporcionar unha alimentación estable.

b. Pequenos condensadores: os condensadores pequenos teñen unha frecuencia resonante máis alta e un radio de filtrado menor, polo que deben colocarse o máis preto posible dos pasadores de chip. Colocalos demasiado lonxe non pode filtrar eficazmente o ruído de alta frecuencia, perdendo o efecto de desacoplamiento. O esquema correcto garante que a eficacia dos pequenos condensadores no filtrado de ruído de alta frecuencia se utiliza completamente.

C. Método de cable de condensadores de desacoplamiento paralelo

Para mellorar aínda máis a integridade da potencia, a miúdo múltiples condensadores de desacoplamiento están conectados en paralelo. O obxectivo principal desta práctica é reducir a inductancia da serie equivalente (ESL) de condensadores individuais mediante conexión paralela.

Cando se paralelan múltiples condensadores de desacoplamiento, débese prestar atención á colocación de VIAS para os condensadores. Unha práctica común é compensar as vías do poder e do chan. O principal propósito disto é reducir a inductancia mutua entre os condensadores de desacoplamiento. Asegúrese de que a inductancia mutua é moito menor que a ESL dun único condensador, de xeito que a impedancia global de ESL despois de paralelo múltiples condensadores de desacoplamiento sexa 1/n. Ao reducir a inductancia mutua, pódese mellorar eficazmente a eficiencia do filtrado, garantindo a mellor estabilidade de potencia.

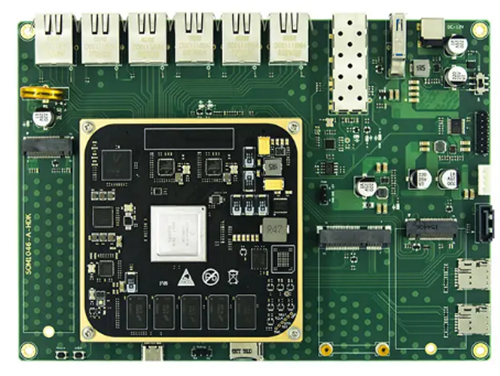

Disposicióne enrutamento de módulos de enerxía, planificación do deseño de planos de capa interior e un manexo correcto da disposición e cableado de chip de enerxía son indispensables no deseño de dispositivos electrónicos. A través dun esquema e enrutamento adecuados, podemos garantir a estabilidade e a eficiencia dos módulos de potencia, reducir a interferencia de ruído e mellorar o rendemento global. Deseño de pilas de capas e segmentación de potencia múltiple optimizan aínda máis as características dos planos de enerxía, reducindo a interferencia de ruído de potencia. O manexo adecuado do esquema de chip de enerxía e os condensadores de cableado e desacoplamiento son cruciais para o control da integridade da enerxía, garantindo unha subministración de corrente estable e filtrado eficaz de ruído, aumento do rendemento e estabilidade do dispositivo.

No traballo práctico, hai que considerar diversos factores como a magnitude actual, o ancho do enrutamento, o número de VIAS, os efectos de acoplamiento, etc. Siga as especificacións de deseño e as mellores prácticas para garantir o control e optimización da integridade do poder. Só deste xeito podemos proporcionar unha oferta de enerxía estable e eficiente para dispositivos electrónicos, satisfacer as crecentes demandas de rendemento e impulsar o desenvolvemento e o progreso da tecnoloxía electrónica.

Shenzhen Anke PCB Co., Ltd

Tempo post: Mar-25-2024